# Fonctionnement collaboratif entre l'IRT St Exupéry et la plateforme PROOF

COS – PROOF 05.10.2022

Fabio Coccetti IRT Saint Exupéry (Toulouse)

fabio.coccetti@irt-saintexupery.com

www.irt-saintexupery.com

- Improve products life cycle

- Enable increased electrification of systems

- Reduce products weight and volume

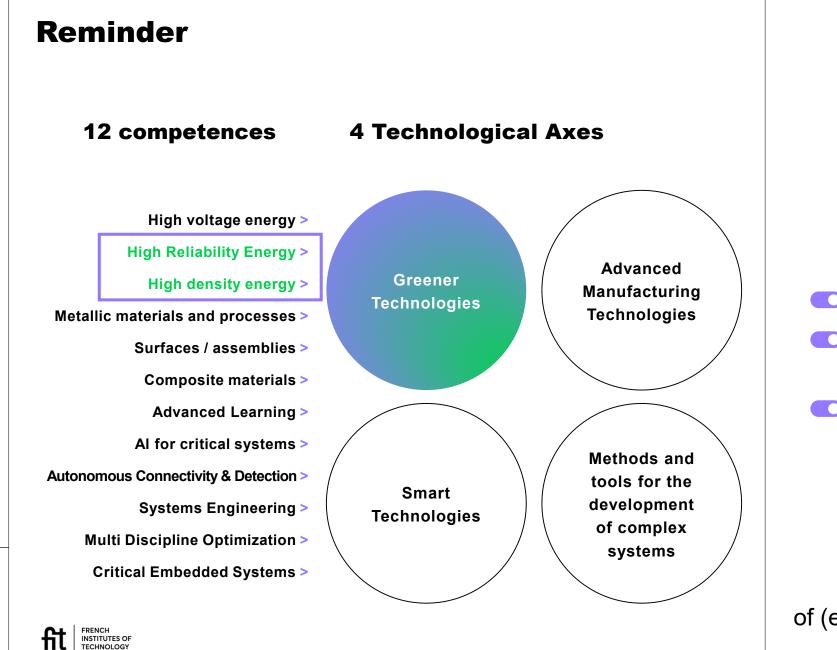

# **Electrification**

of (embedded) systems and functions !

р а g e

р

# 10/12/2022

р

а

SAINT FYUDÉD

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

**PMEs**

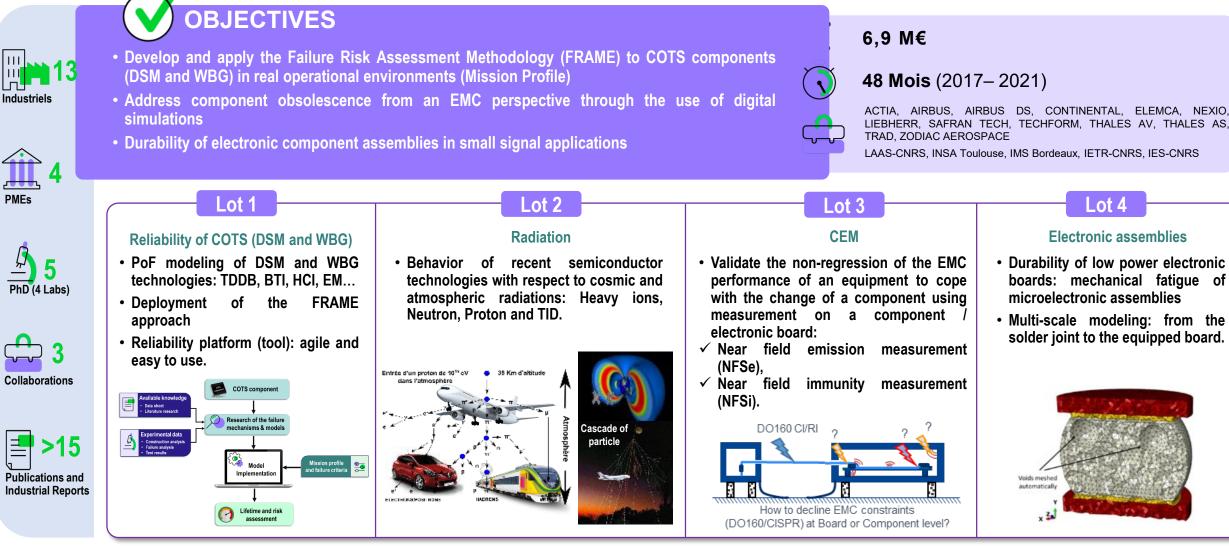

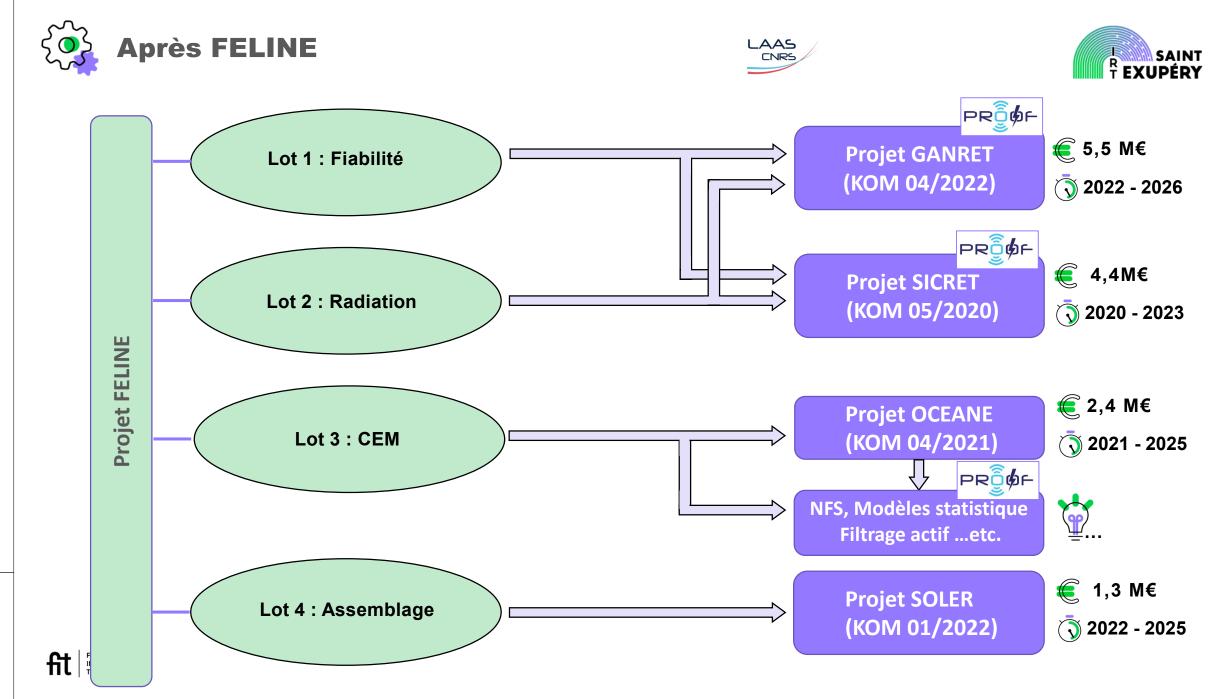

# FELINE : Fiabilité ÉLectronique INtégréE

\_ot 4

**Electronic assemblies**

next move

р а

g

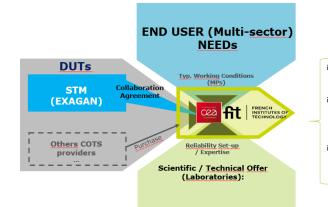

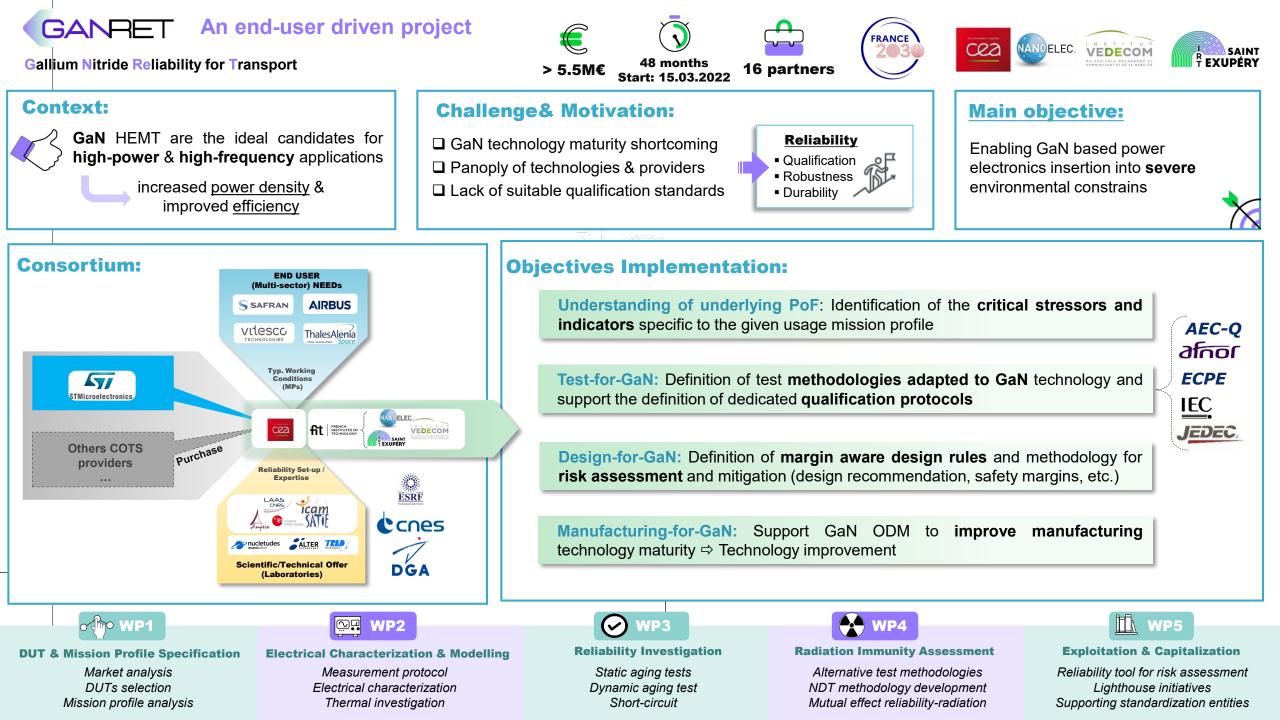

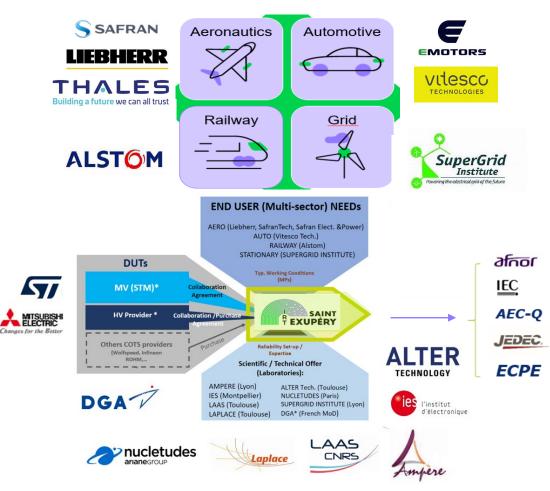

# GaNRET GaN (Power Transistor) Reliability Evaluation for Transport

*Project Set-up Team:*

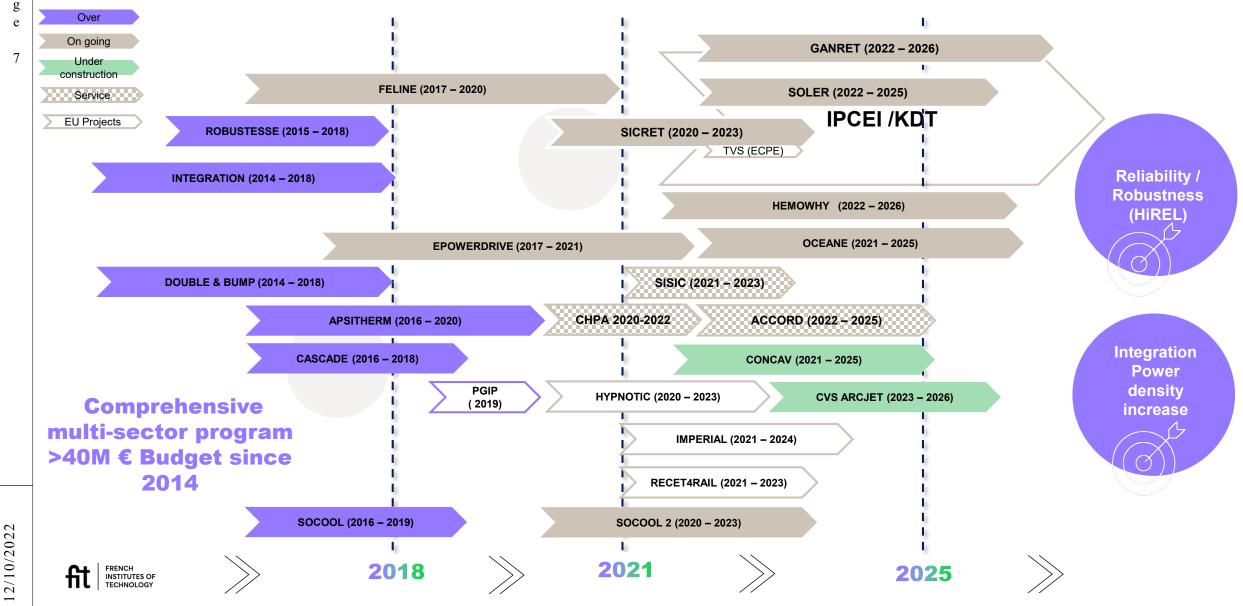

TENTATIVE: BUDGET: ~ 10 M€ - DURATION: 48MM Start Date: 2022-Q1

\* Main Challenges:

- PoF <u>not-well understood</u> / established

- Panoply of (<u>not mature</u>) technologies (e/d mode)

- Design rules and test protocol for advanced (embedded) packaging

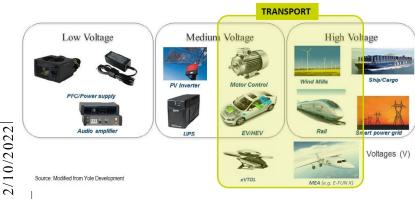

Application domain:

Low Voltage **Medium Voltage High Voltage PFC / Power supply PV** inverter Motor control Ships GaNRET **Power Grid** Application Domain Space Power Wind energy EV/HEV UPS Train transportation Audio Amplifie < 200V 1.2kV 1.7kV 600V 900V 3.3kV >6.5kV GaN (Low/Medium Voltage) SiC (Medium/High Voltage)

PFA AMOBILITES

# SiCRET

12

### Silicon Carbide (MOSFET) Reliability Evaluation for Transport

#### End-user oriented project focused on

- Test for SiC : Definition of test procedures and methodologies adapted to user mission profiles (dedicated SiC technology qualification)

- Design for SiC : Establishment of mitigation solution (with respect to enduser MP) such as design recommendation (e.g.Derating rules for safety margins, etc.)

### Context

- Future electrification technologies require drastic improvements of power electronics. SiC MOSFET are key enablers

- Reliability/ lifetime are mandatory for SiC adoption Convergence of applications / high reliability requirements

- Strong investment of industry is necessary to adapt qualification approach and design rules

\*ANR: French National Research Agency

36 months (May 2020 to Apr 2023)

### **Project members and partners**

SAINT

T EXUPÉRY

FRANCE

20)%

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

FRENCH

INSTITUTES OF TECHNOLOGY

fil

## **SICRET Program: What's NEXT!**

**Discussion starting on 2022-Q2**

**Qualification Test plan Definition** (Proposal)

Guidelines definition (SOA, Design rules, ...)

### At <u>Power Module</u> level including other studies/tests.

- Low pressure, humidity,

- Thermal management (power cycling, temperature cycling)

- EMC emission/immunity

### Enhanced by the collaboration with STM <u>(associate Partner of the project)</u>

Source: ST Microelectronics

At discrete component level

**SiCRET**

arbide Reliability Evaluation for Transpo

OHI

Sicret

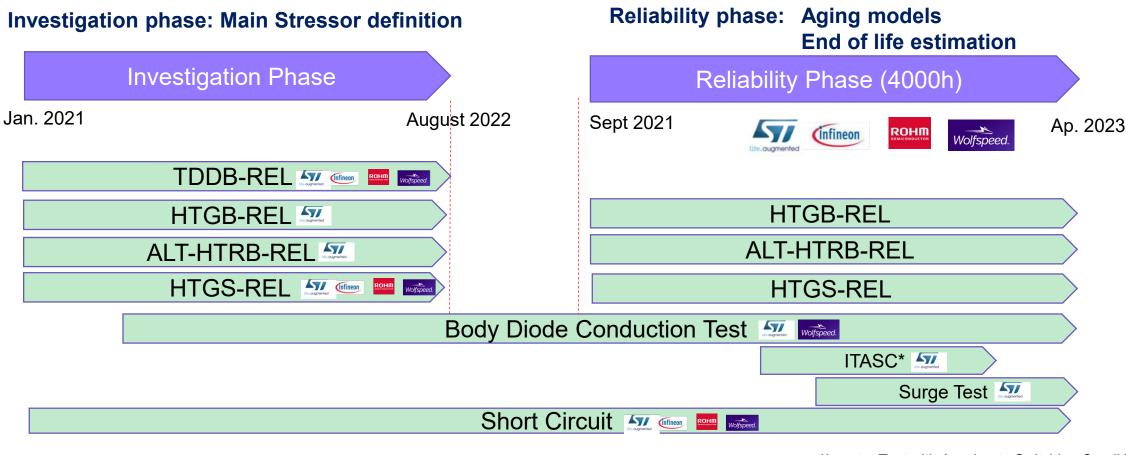

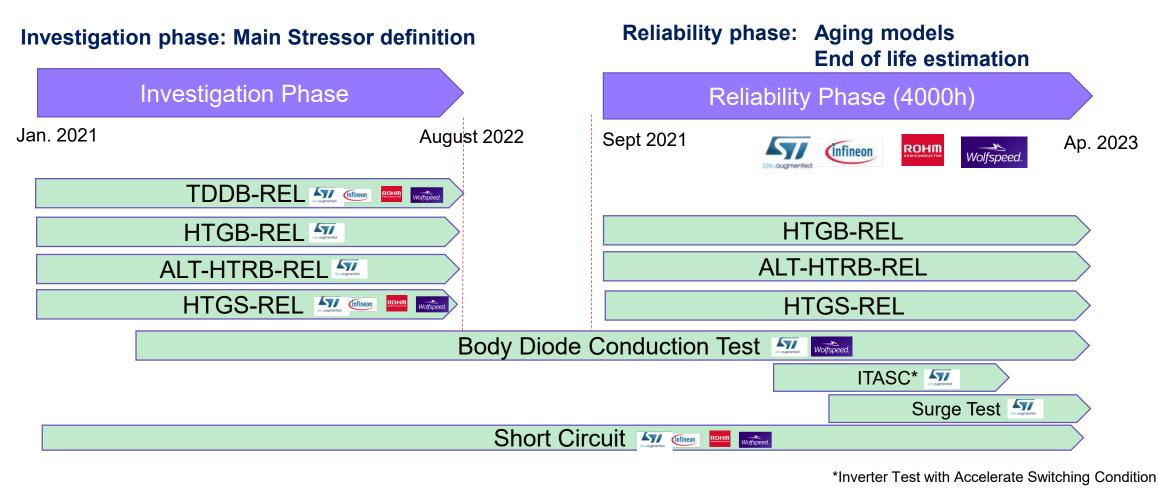

## **Medium Voltage Reliability Test Plan**

Optimization Methodological Approach (costs-effectiveness)

\*Inverter Test with Accelerate Switching Condition

« REL »  $\rightarrow$  above usual qualification time, up to EoL or degradation to derive ageing law

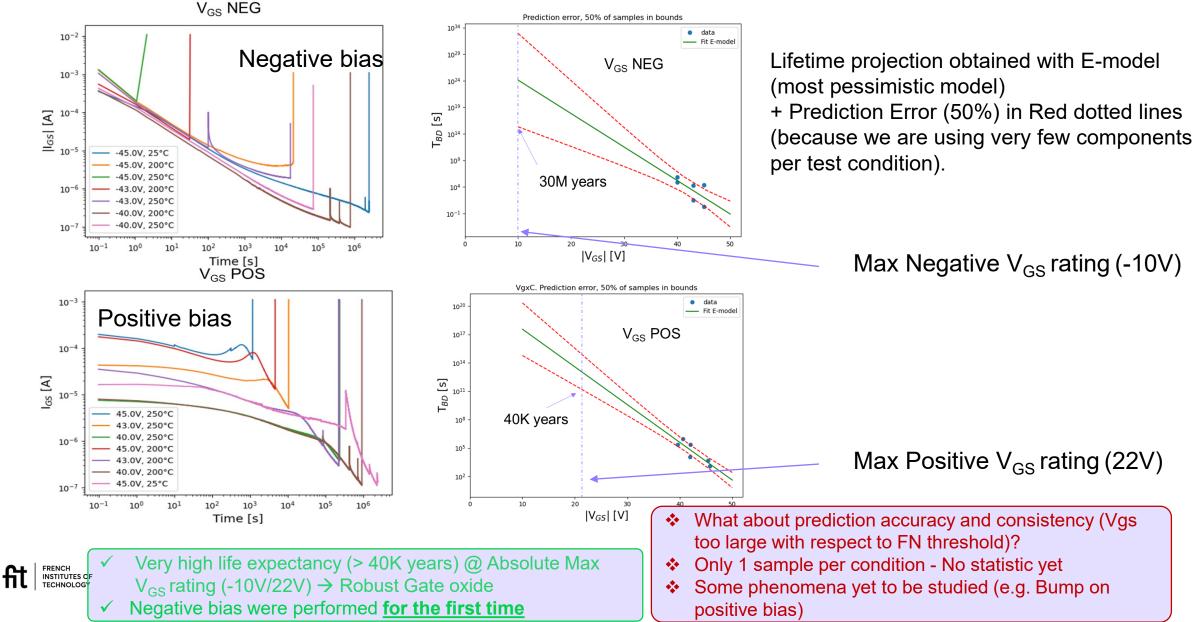

## **Investigation Test Plan: TDDB-REL Results**

Investigation on TDDB for gate oxide lifetime prediction (STM-G2)

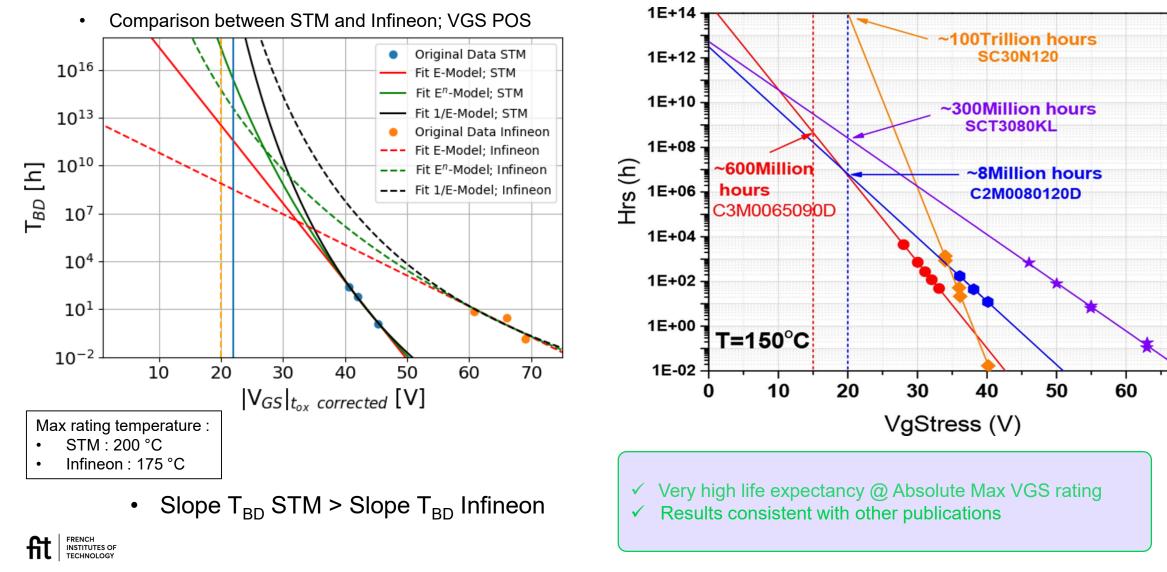

### Lifetime projections of gate oxide comparison

70

STM vs Infineon Trench and vs state of the art

16

2/10/2022

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

Jun Wang and Xi Jiang,"Review and analysis of SiC MOSFETs' ruggedness and reliability" IET Power Electron., 2020, Vol. 13 Iss. 3, pp. 445-455 © The Institution of Engineering and Technology 2019

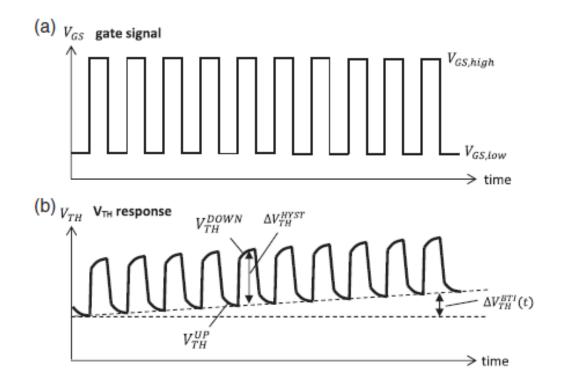

# **Need of reliability insight**

at semiconductor (die) level

T. Aichinger, et al., Microelectronics Reliability 80 (2018) 68-78.

# How to discriminate between reversible (recovery) and not reversible phenomena (aging) !!

Tt FRENCH INSTITUTES OF TECHNOLOGY

### **Vth Characterization**

VTH protocol definition

#### $V_{th}$ measurement @ Id = 1 mA Unipolar **Bipolar JEDEC** STM / ALTER V<sub>GS</sub> $V_{GS}$ D $I_{d}(V_{GS})$ $1 \text{ms} < t_{(+)} < 100 \text{ ms}$ G V<sub>GS(+)</sub> $\rightarrow$ V<sub>GS(+)</sub> DUT Preconditioning t<sub>Vth</sub> < 10 ms S $I_{G}$ 4 Time t<sub>float</sub> < 10 ms Time V<sub>GS(-)</sub> **Industrial Setup Academic Labs** $V_{GS}$ setup D Preconditioning V<sub>GS(+)</sub> $V_{\rm DS} = 0 V$ G DUT $V_{DS} = V_{GS}$ $V_{GS}$ SICRET S V<sub>GS(-)</sub> Time V<sub>DS</sub> FRENCH INSTITUTES OF TECHNOLOGY fit 5 Related to B1505A 0 © IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

2/10/2022

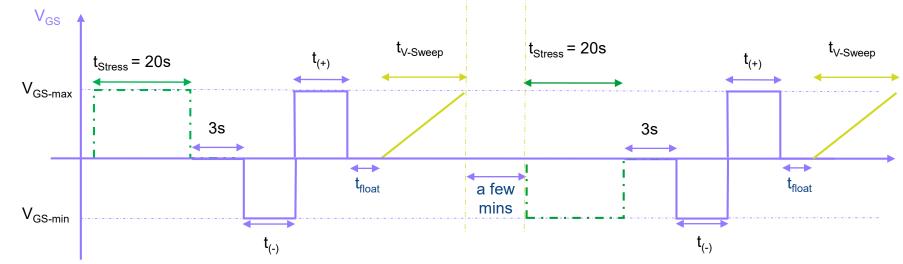

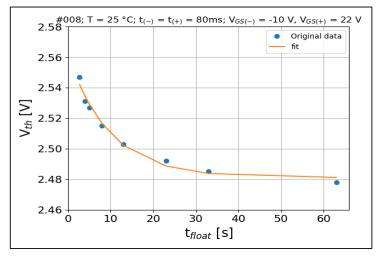

# Influence of pre-conditioning on Vth measurement and time for read-out

FRENCH INSTITUTES OF TECHNOLOGY

fi

#### t<sub>float</sub> delay impact on the Vth value

### Influence of positive / negative stress

Pre-conditioning robustness against device "normal operation history"

| Pre-conditionning<br>Method with tfloat=0 | ∆V <sub>th-pos</sub><br>Positive<br>Stress of 20s | ∆V <sub>th-neg</sub><br>Negative<br>Stress of 20s | V <sub>th</sub> (V) |

|-------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------|

| Positive only                             | 77 mv                                             | 144 mV                                            | 3.19                |

| Negative + Positive                       | 1 mV                                              | 14 mV                                             | 3.15                |

LAAS

CNRS

## **Vth Characterization**

Example of stable Vth measurement

Random behaviors in the case of Vth measurements without preconditioning

fitench INSTITUTES OF TECHNOLOGY

### With SiCRET/JEP184 preconditioning

- Very stable and robust measurement of Vth (main aging indicator)

- $\checkmark$  True monitoring of Vth degradation

- ✓ SiCRET Vth method deployable on ALL environment (Research / Industry)

2/10/2022

## Medium Voltage Reliability Test Plan

Optimization Methodological Approach (costs-effectiveness)

« REL »  $\rightarrow$  above usual qualification time, up to EoL or degradation to derive ageing law

### **HTRB : Vth (1mA) drift results - ST Gen 2**

Vth characterization

t(-)= 80 ms

t(+)= 5s t<sub>V-Sweep</sub> = 200ms

V<sub>GS</sub>

V<sub>GS(+)</sub>

V<sub>GS(-)</sub>

VDS

5 0

Comparison between Investigation / Reliability

| Investigation phase Results |          |       |        |        |        |          |         |        |        |

|-----------------------------|----------|-------|--------|--------|--------|----------|---------|--------|--------|

| Conditions                  |          |       |        |        |        | Stress T | ime [h] |        |        |

|                             | т        | VGS   | VDS    | 0      | 24     | 168      | 336     | 500    | 1000   |

| SN141_R                     | ef       |       |        | 3.00 V | 1.5 %  | 0.9 %    | -0.1 %  | 2.5 %  | -0.0 % |

| SN56                        | 1 25 °C  | -10 V | 1400 V | 3.21 V | -0.8 % | 0.3 %    | -0.2 %  | 1.4 %  | -0.7 % |

| SN55                        | 9 25 °C  | -5 V  | 1400 V | 2.95 V | -0.8 % | 0.0 %    | -0.4 %  | 0.2 %  | -0.4 % |

| SN56                        | 6 25 °C  | -5 V  | 1500 V | 3.14 V | 0.1 %  | 0.1 %    | -0.4 %  | 0.8 %  | -0.6 % |

| SN56                        | 2 25 °C  | 0 V   | 1500 V | 2.93 V | -1.0 % | -0.8 %   | -1.2 %  | -0.4 % | -0.8 % |

| SN53                        | 8 125 °C | -10 V | 1400 V | 3.06 V | 1.2 %  | 1.4 %    | 0.6 %   | 2.1 %  | 1.3 %  |

| SN54                        | 8 125 °C | -5 V  | 1400 V | 3.19 V | 1.8 %  | 2.2 %    | 1.4 %   | 3.0 %  | 1.0 %  |

| SN55                        | 8 125 °C | -5 V  | 1500 V | 3.05 V | 1.8 %  | 2.7 %    | 1.0 %   | 2.5 %  | 0.8 %  |

| SN53                        | 9 125 °C | 0 V   | 1500 V | 3.07 V | -0.9 % | -1.2 %   | -1.2 %  | -0.0 % | 0.7 %  |

| SN53                        | 5 200 °C | -10 V | 1500 V | 3.11 V | 1.2 %  | 1.8 %    | 1.9 %   | Failed | Failed |

| SN49                        | 8 200 °C | -5 V  | 1400 V | 3.24 V | 1.5 %  | 0.3 %    | -0.0 %  | Failed | Failed |

| SN53                        | 6 200 °C | -5 V  | 1500 V | 3.07 V | -0.4 % | -0.3 %   | -1.5 %  | -0.2 % | 1.0 %  |

| SN47                        | 9 200 °C | 0 V   | 1400 V | 3.00 V | -0.7 % | -1.3 %   | -1.1 %  | -0.5 % | 1.2 %  |

- No significant drift on any parameter  $\checkmark$

- 2 failures analyzed. \*

#### No conclusion on these failures \*\*

FRENCH fit INSTITUTES OF TECHNOLOGY

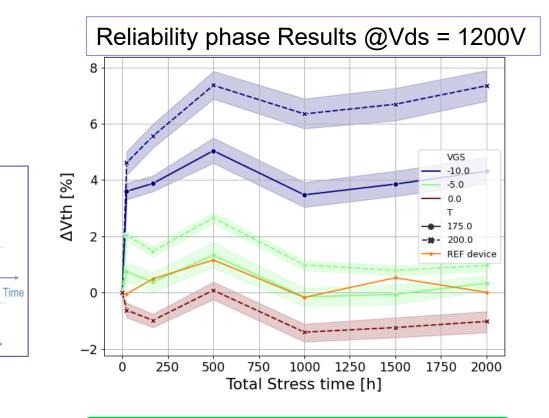

- Vth drift < 8%

- Vth variation is mainly due to negative Vgs  $\checkmark$

- Very Robust to HTRB  $\checkmark$

No Ageing law regarding static Vds voltage

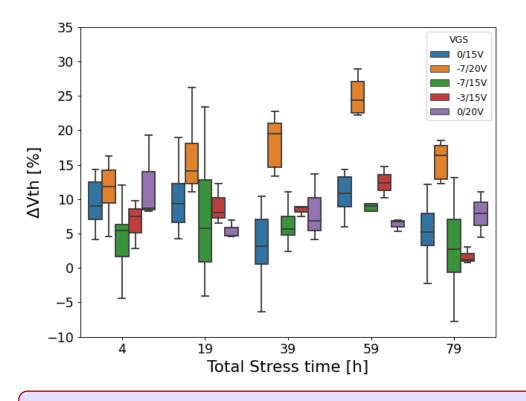

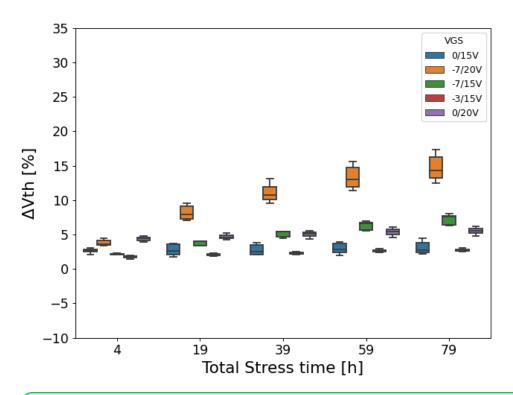

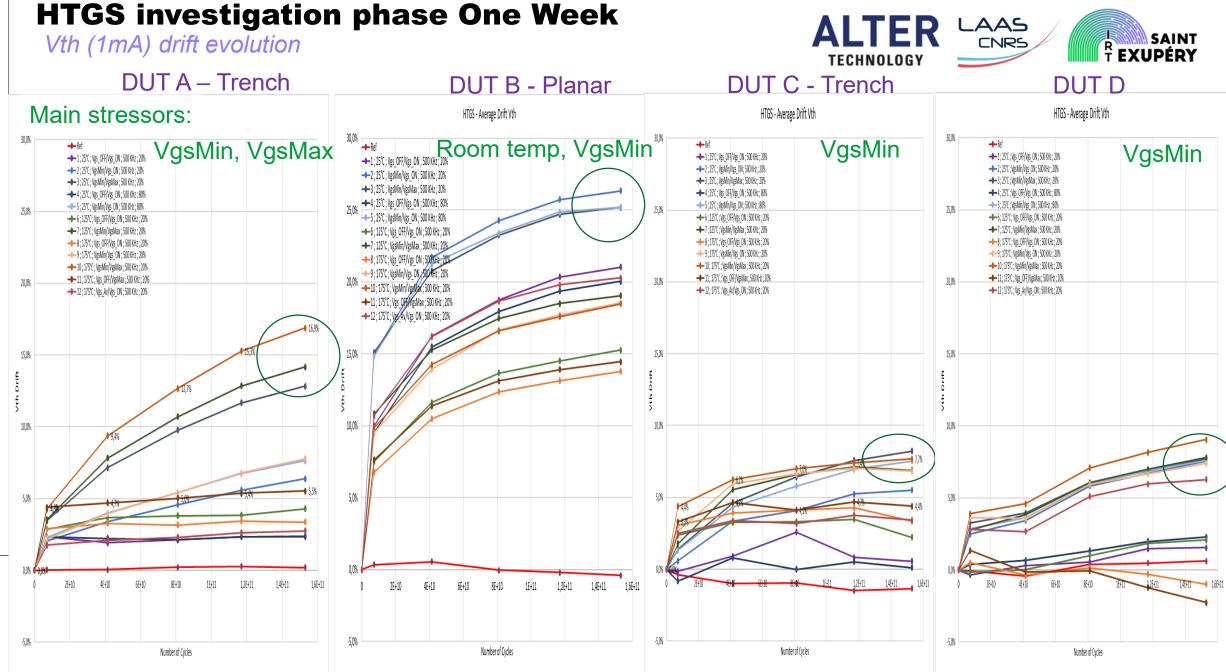

### **HTGS investigation phase One Week**

Same DoE for each Manufacturer (excepted Vgs values adapted per datasheet)

### **Glossary (from datasheet)**:

- Vgs,on: Recommended turn-on gate voltage

- Vgs,off: Recommended turn-off gate voltage

- VgMax: Max positive transient voltage

- VgMin: Min negative transient voltage

- VgsAv: Average value between VgsMin and Vgs,OFF

| HTGS DoE     | Gate voltage     | Temperature | Frequency | Duty cycle | Qty |

|--------------|------------------|-------------|-----------|------------|-----|

| Condition 1  | Vgs,off / Vgs,on | 25°C        | 500 kHz   | 20%        | 3   |

| Condition 2  | VgsMin /Vgs,on   | 25°C        | 500 kHz   | 20%        | 3   |

| Condition 3  | VgsMin / VgsMax  | 25°C        | 500 kHz   | 20%        | 3   |

| Condition 4  | Vgs,off / Vgs,on | 25°C        | 500 kHz   | 80% (*)    | 3   |

| Condition 5  | VgsMin / Vgs,on  | 25°C        | 500 kHz   | 80% (*)    | 3   |

| Condition 6  | Vgs,off / Vgs,on | 125°C       | 500 kHz   | 20%        | 3   |

| Condition 7  | VgsMin / VgsMax  | 125°C       | 500 kHz   | 20%        | 3   |

| Condition 8  | Vgs,off / Vgs,on | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 9  | VgsMin / Vgs,on  | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 10 | VgsMin / VgsMax  | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 11 | Vgs,off / VgsMax | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 12 | VgsAv / Vgs,on   | 175°C       | 500 kHz   | 20%        | 3   |

Note (\*): DC = 80% means 80% ON, 20% OFF

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

# **STM Gen 2 – Investigation and Reliability Conclusions**

# <u>HTRB</u>

| No significant drift with Drain Voltage<br>Vth variation is due to VGS (-10V)<br>→ very robust to HTRB<br>→ next studies : DRB "Dynamic Reverse Bias"                                        | <ul> <li>Maximum available test bench frequency (500 KHz)</li> <li>Maximum and recommended Vgs values per datasheet</li> </ul>                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HTGB                                                                                                                                                                                         | - Temperature influence (up to maximum rating value)                                                                                                                                                   |

| <ul> <li>The main stressors causing V<sub>th</sub> and R<sub>DSon</sub> drifts are related to :</li> <li>Temperature (200 °C).</li> <li>Gate voltages (specially if out of spec).</li> </ul> | <ul> <li>∆Vth<sub>HTGB</sub> (static stress) &lt; ∆Vth<sub>HTGS</sub> (dynamic stress)</li> <li>→ Dynamic stress is worse than the static one</li> <li>Next step : find aging laws for HTGS</li> </ul> |

| <ul> <li>Vth drift less than 10% after 10 years<br/>with an Automotive MP (Inverter)</li> </ul>                                                                                              |                                                                                                                                                                                                        |

HTGS

2/10/2022

FRENCH

INSTITUTES OF TECHNOLOGY

fil

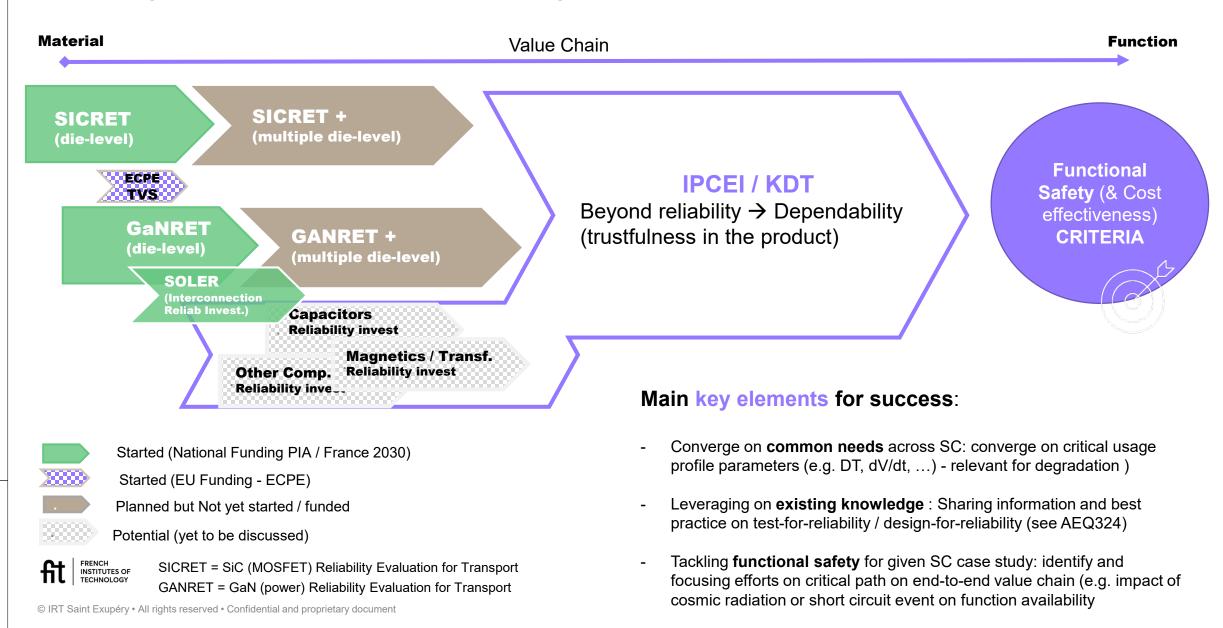

## **Synergy between collaborative Project**

Toward dependable - "Trustfull" - WBG based power electronics

2/10/2022

### **Lighthouse activities**

### **Connecting with Specialized Networking**

In order to engage and establish a high level scientific and technical discussion with the most pertinent stakeholders, this task will be organized in three main types of activities:

- To organize focused workshops with industrial and/or scientific entities.

- Identify and stimulate the discussion and exchange with specialized professional networks such as the European Center for Power Electronics (ECPE) in Europe or the Center for Power Electronic Systems (CPES) in USA or their counterparts in other regions.

Exchange and support international normalization bodies currently dealing with standardization of emerging WBG technologies, such as JEDEC, AEC, AFNOR, IEC...

Sicret

### **Conclusions and Perspectives**

- PROOF is an important part of the Regional / National R&D asset and roadmap (toward electrification)

- IRT-SE consider PROOF as an essential partner to reach critical mass in WBG reliability projects  $\checkmark$

- Engage a discussion on evaluate how a more long term collaboration can be done (after PROOF PRRI)

- PROOF Scientific support (expertise and equipment) instrumental in running projects (e.g. SICRET, GANRET, ...)

- Much more is ongoing and has to come yet:  $\geq$

- Aging degradation monitoring by LFN (!?)

- Dynamic behavior robustness (e.g. DRB, DBV, ...) by ESD techniques (!?)

- Interconnection degradation monitoring by RF detection (!?)

- Device junction temperature for thermal monitoring and management (NRTW Rouen March 2023)

- Use of NFS techniques to enhance EMC/I design (from device to board and back)

- ...

Sicret

### **Acknowledgments:**

**Industrial Secondments**: M. Piton (ALSTOM) – R. Meuret S. Azzopardi (SAFRAN) – H. Aubertin (VIESCO) – – O. Perrotin (ALTER) – A. Dourier (CONTINENTAL) - A. Bensoussain (TAS) - O. Crepel (AIRBUS) – J.J Fabre (ACTIA)

Industrial & Institutional Experts: J. Toulze (AIRBUS) – J.F. Besnier (CONTINENTAL) – C. Moreau (DGA) – G. Bascoul (CNES) - B. Asllani (SGI) – L. Allirand (VITESCO) – F. Miller (Nucletudes) - J.P. Carayon , M. Nüber (LIEBHERR) – F. Thillac (ALTER)

STMicroelectronics: E. Merli, R. Nicoloso, M. Ferrara, F Di Giovanni, M. Saggio, F. Pintacuda, / P. Lolies, J.B. Moreau, E. Moreau ...

Accademic Advisors: A. Touboul, V. Pouget, A. Michez (IES) - F. Richardeau (LAPLACE) - D. Trémouilles (LAAS) – H. Morel (AMPERE) – A. Bravaix (ISEN) - H. Freemont – A. Garzia (IMS)

**IRT personnel**: D. Hachem - H. Hamad - H. Rizk - Y. Barazi – A.J. De Oliveira, S. Chetaui – E. Ben Romdhane - T. Houret - B. Cogo – G. Second – D.H. Tran – L. Rocherons; S. Serpaud, M. Zerarka, V. Rustichelli, J.M. Reynes, P. Kreczanik, P. Frey, R. Riva, P. Roumanille, M. Matmat, C. Ngom, D. Alejo, L. Bourgeois