### Fault Pathologies caused by Moore's Law, and Remedies

2011/07/03

Nobuyasu Kanekawa Hitachi Research Laboratory, Hitachi, Ltd.

© Hitachi, Ltd. 2011. All rights reserved.

### Contents

- 1. Fault Pathologies caused by Moore's Law

- 2. Intra-Board Redundancy

- 3. On-chip Redundancy

- 4. Conclusions

#### Contents

#### 1. Fault Pathologies caused by Moore's Law

- 2. Intra-Board Redundancy

- 3. On-chip Redundancy

- 4. Conclusions

HITACHI

Inspire the Next

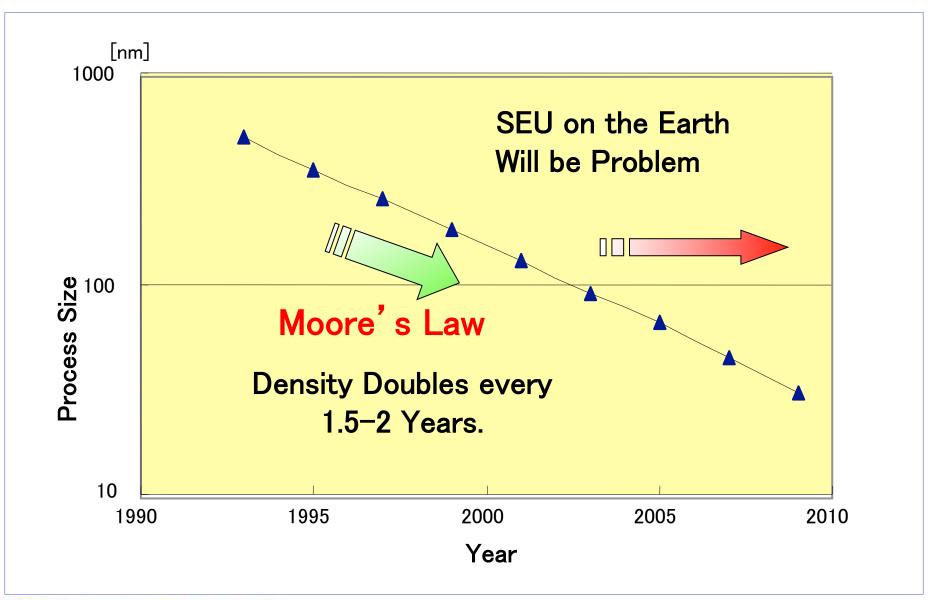

## Moore's Law

HITACHI Inspire the Next

Integration of Semiconductor Causes

→ Decrease Funnel Area (Reduce Error Rate)

Decrease Critical Charge (Increase Error Rate)

→ Increase Error Rate in Overall

Error Rate: x 1.5–2.0/Generation

•Memory Volume x  $n \rightarrow \#$  of Upset x n

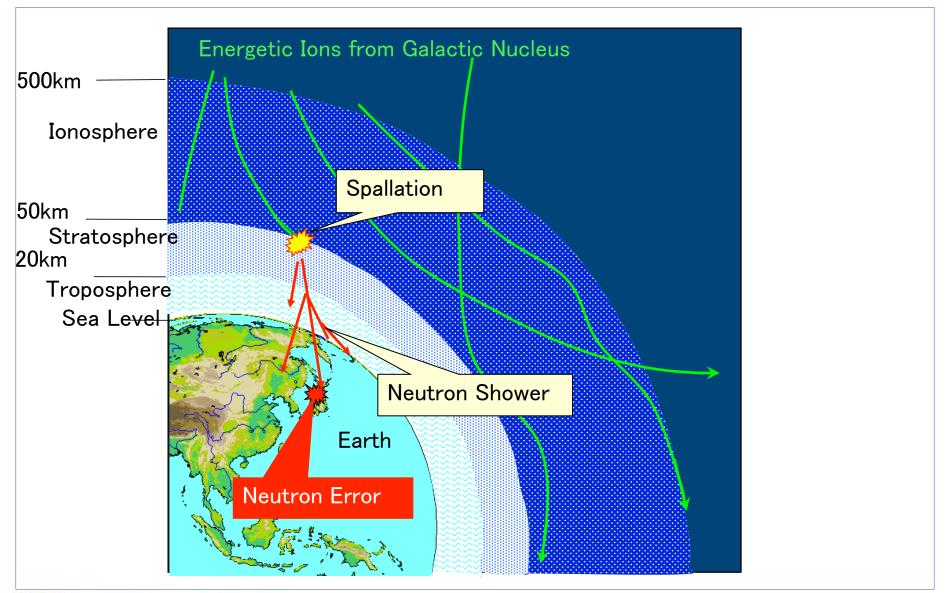

#### **Cosmic Neutron Induced SEU Mechanism**

Integration of Semiconductor Causes

```

Higher Clock Frequency

```

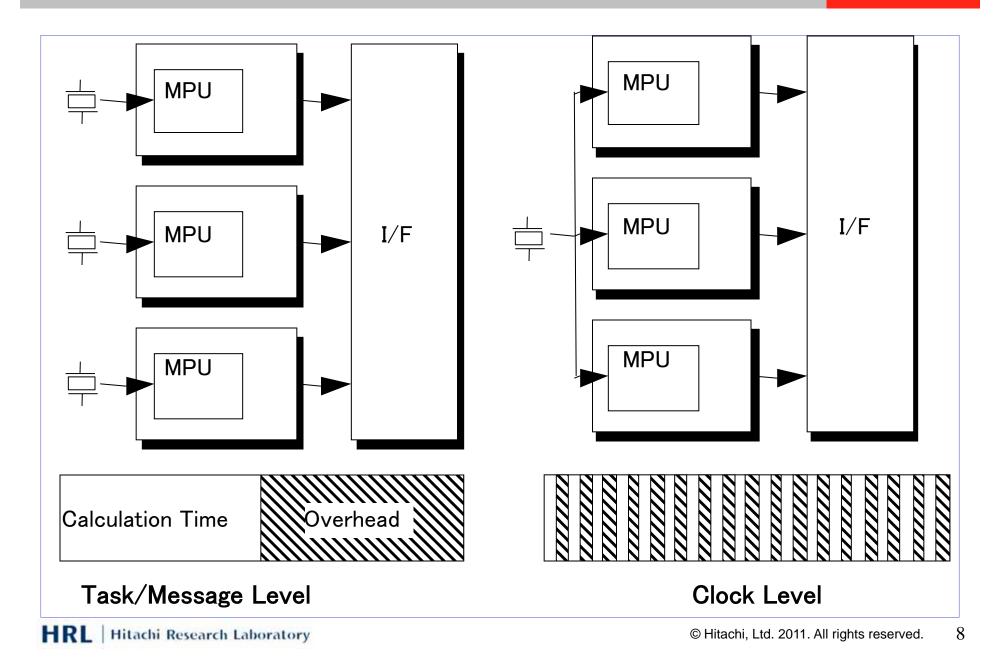

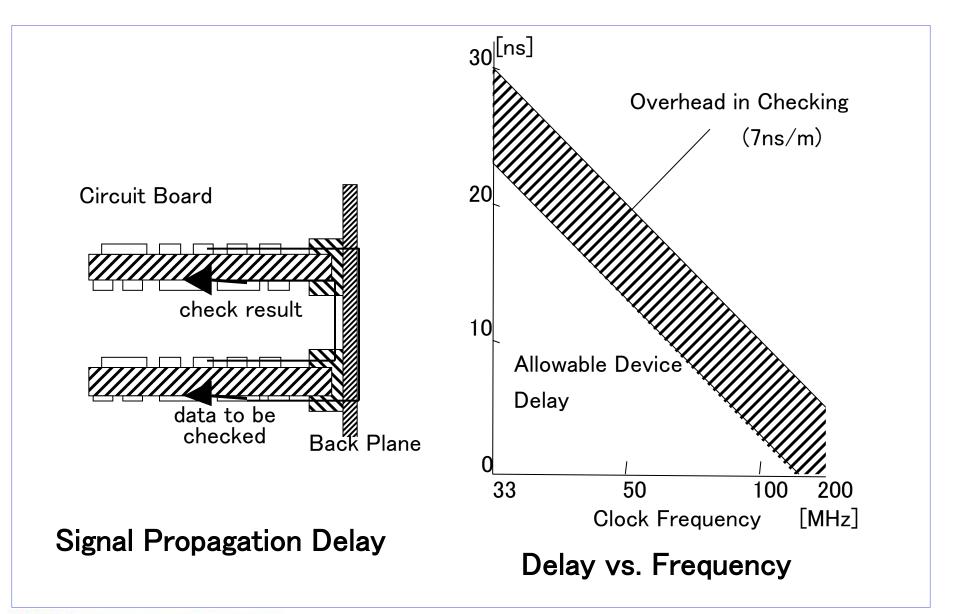

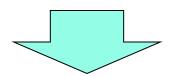

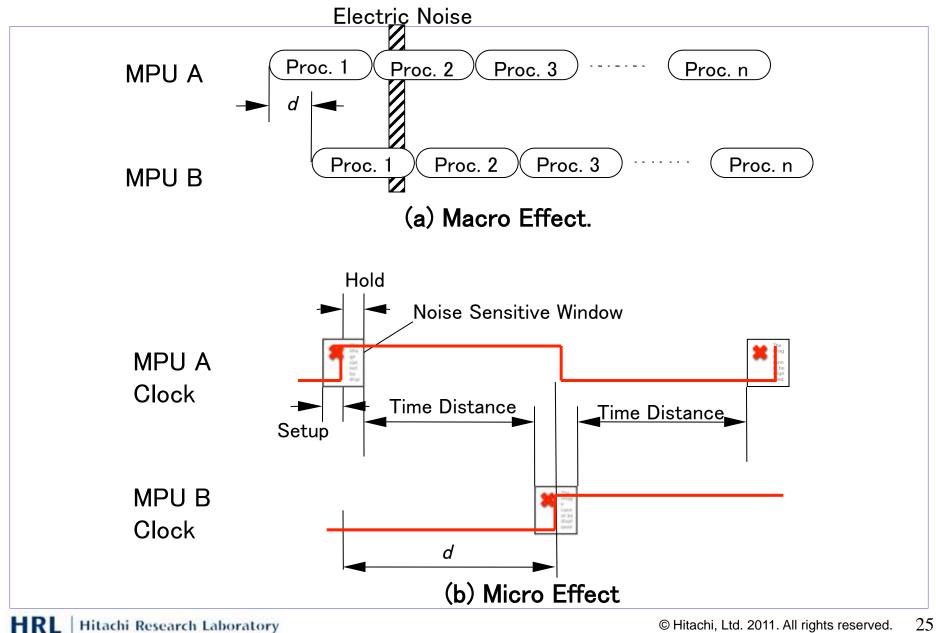

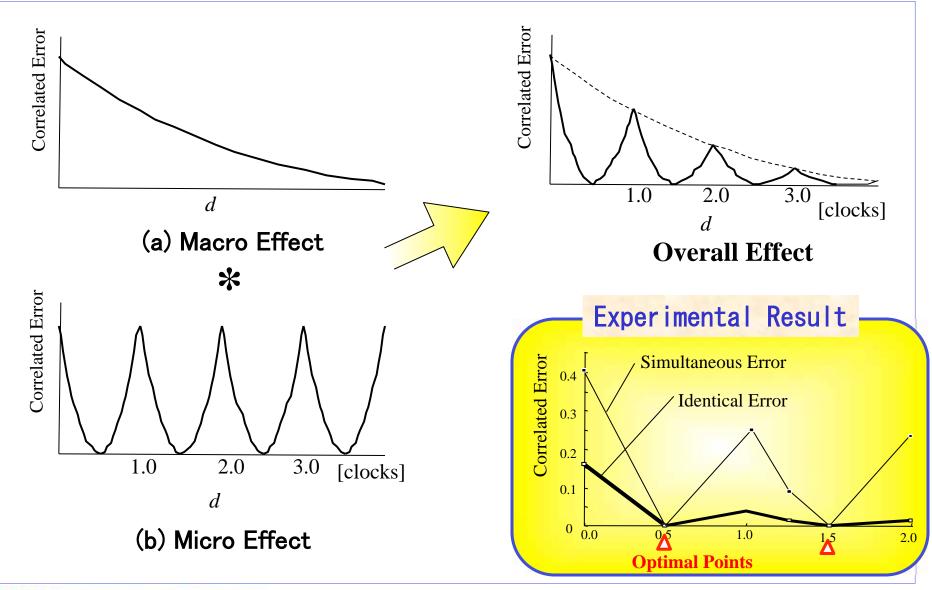

Consideration for Synchronization among Redundant Subsystems will be Indispensable

- Propagation Delay among Redundant Subsystems vs.

- Maintenance-ability (Replace-ability) of Redundant Subsystems

# Synchronization and Overhead

### Synchronization and Overhead

HITACHI

Inspire the Next

Integration of Semiconductor Causes

Higher Clock Frequency Lower Power Supply Voltage →Larger Noise Intensity →More Noise Sensitive

Consideration for Electro-Magnetic Disturbances (EMC, Power Integrity) will be Indispensable

- Terrestrial Neutron induced SEU's

- Synchronization Problem

Intra-Board Redundancy On-chip Redundancy

### Contents

#### 1. Fault Pathologies caused by Moore's Law

#### 2. Intra-Board Redundancy

- 3. On-chip Redundancy

- 4. Conclusions

## Synchronization and Overhead

### Intra-Board Redundancy

HITACHI Inspire the Next

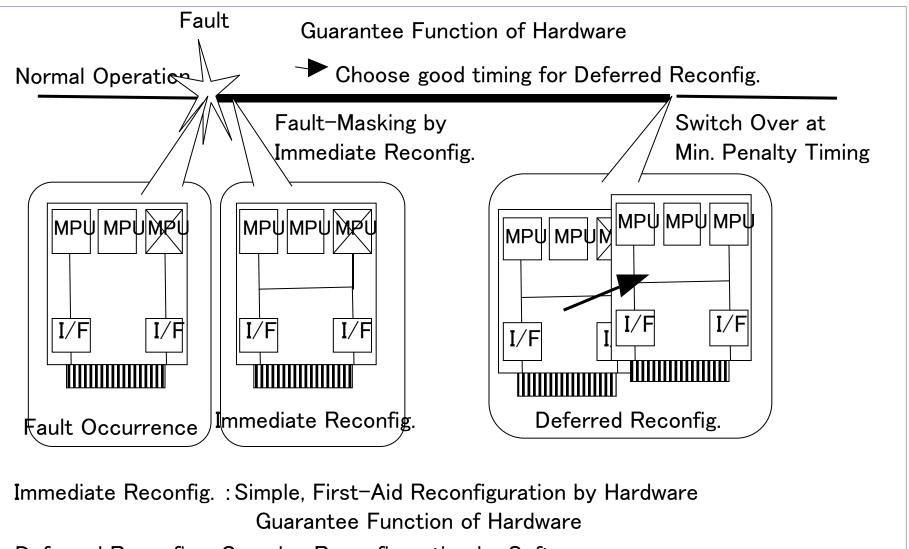

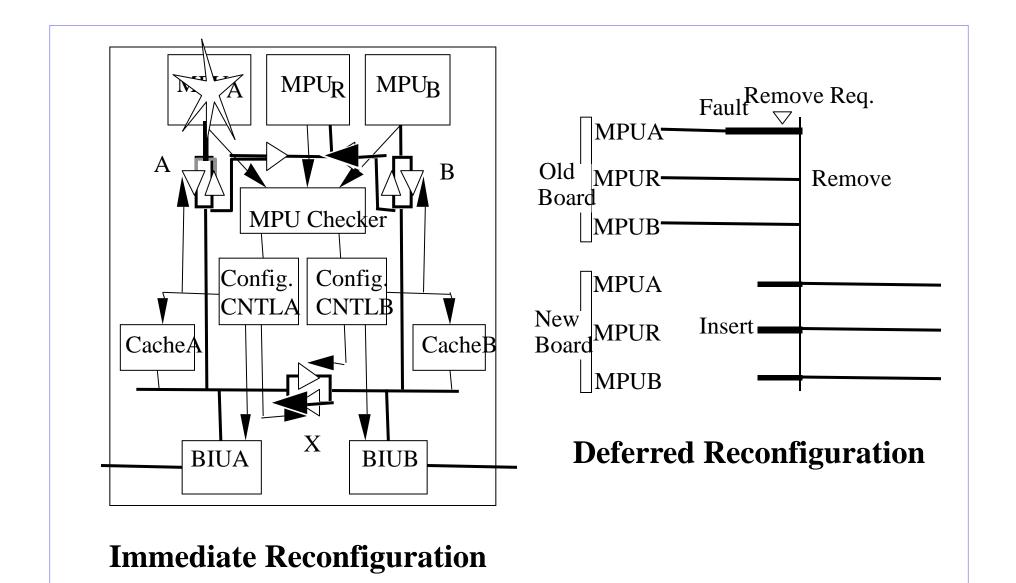

# Immediate/Deferred Reconfiguration

Deferred Reconfig. : Complex Reconfiguration by Software

Simplify Hardware

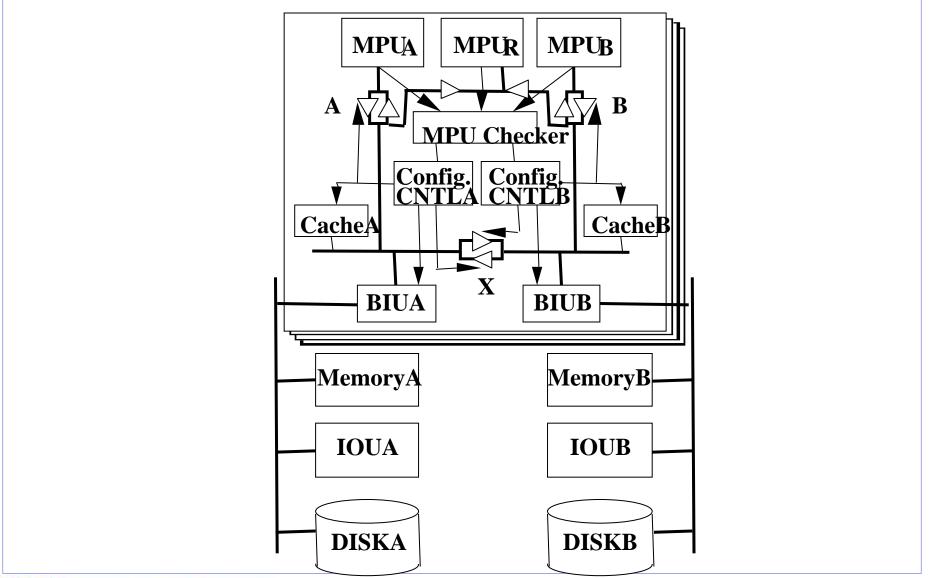

#### **TPR** Architecture

\*Triple Processor & check Redundancy

### Immediate/Deferred Reconfiguration

Inspire the Nex

#### **QPR** Architecture

HRL | Hitachi Research Laboratory

### Contents

- 1. Fault Pathologies caused by Moore's Law

- 2. Intra-Board Redundancy

- 3. On-chip Redundancy

- 4. Conclusions

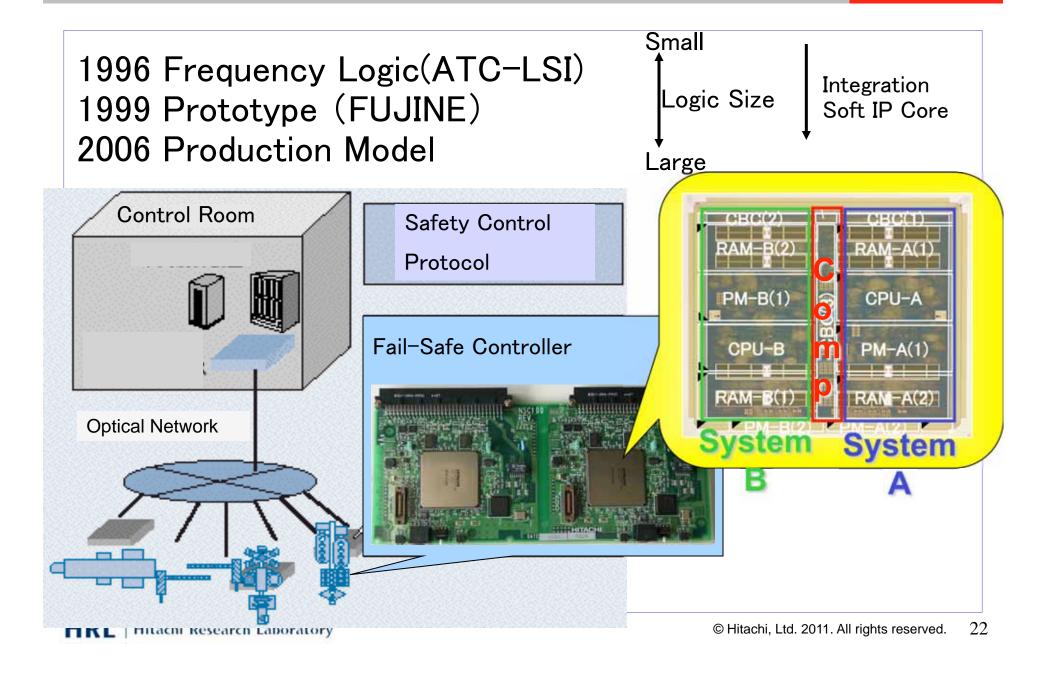

# Integration of LSI →Needs for SEU Countermeasure →Seeds for Multi-Core MPU

# Electronic Control (Train Automotive) →Needs for Dpendability

# Safety Micro-controller (On-Chip Redudancy)

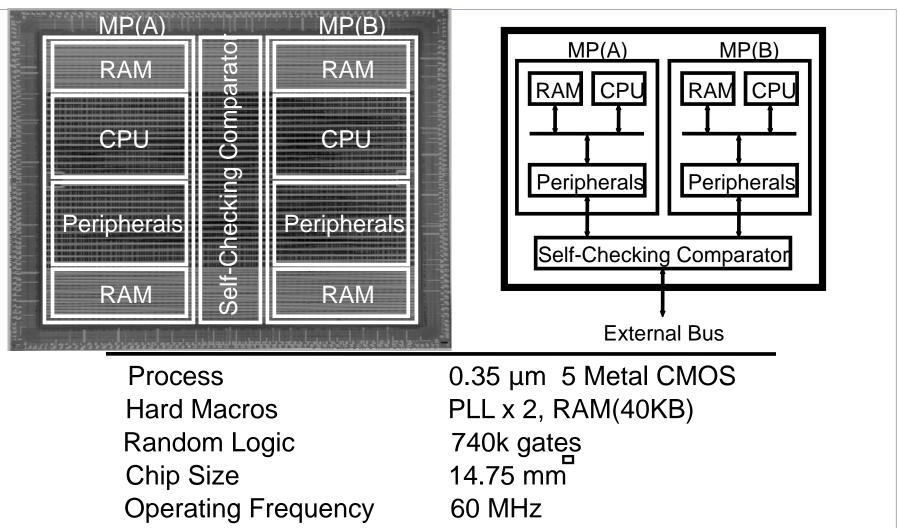

### Safety Micro-Controller Prototype (FUJINE)

2.6W @ 60MHz

479pin BGA

Power Dissipation Package

© Hitachi, Ltd. 2011. All rights reserved. 21

HITACHI Inspire the Next

#### Safety Micro-Controller

HITACHI Inspire the Next

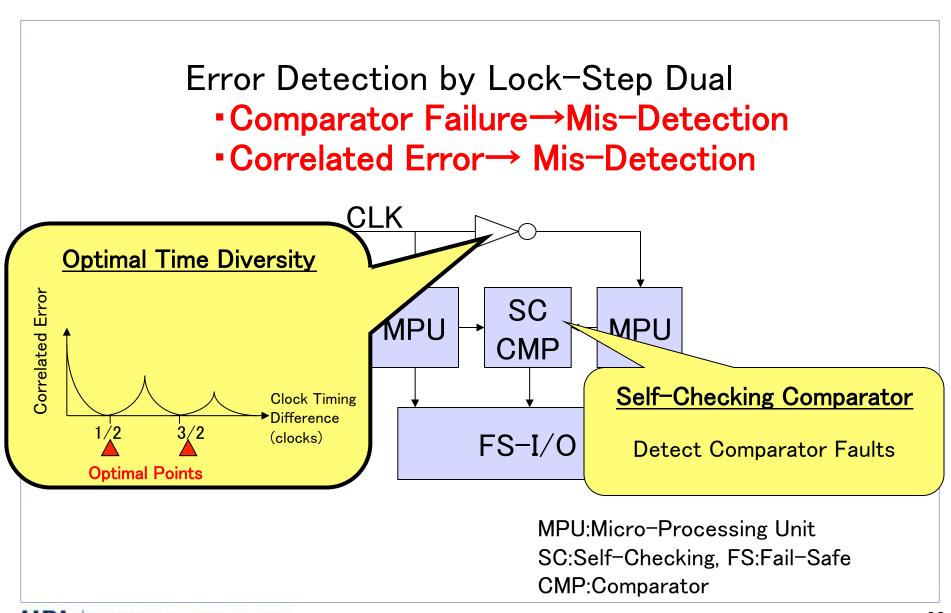

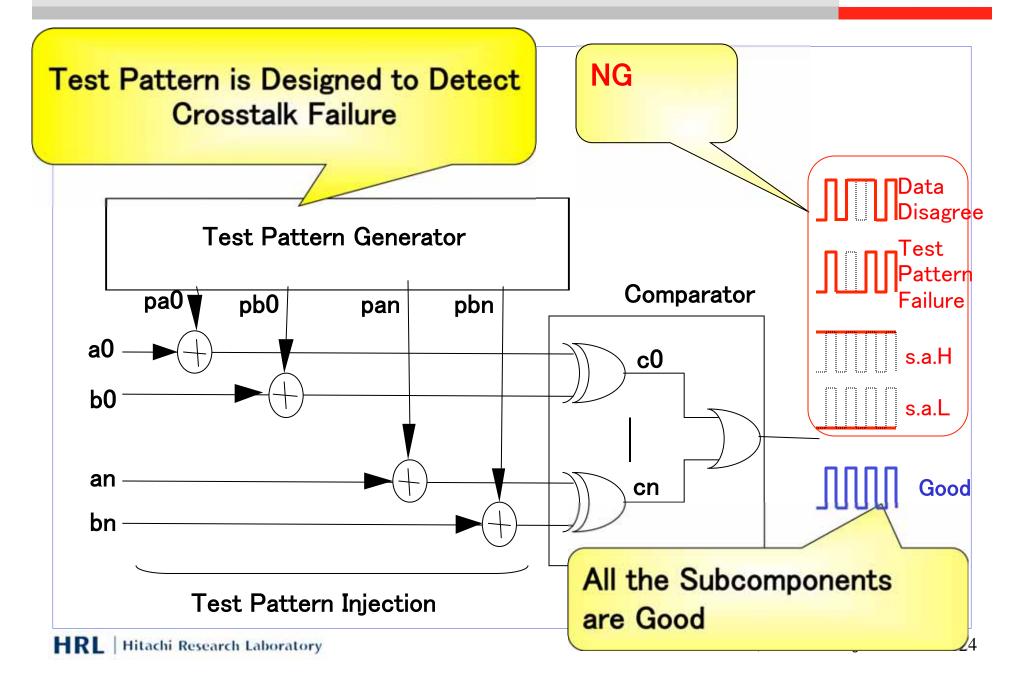

### **Self-Checking Processor**

Inspire the Nex

### Self-checking Comparator

### **Effect Of Time Diversity**

HITAC Inspire the Next

### **Effect Of Time Diversity**

HITACHI Inspire the Next

### Contents

- 1. Fault Pathologies caused by Moore's Law

- 2. Intra-Board Redundancy

- 3. On-chip Redundancy

#### 4. Conclusions

### Conclusions

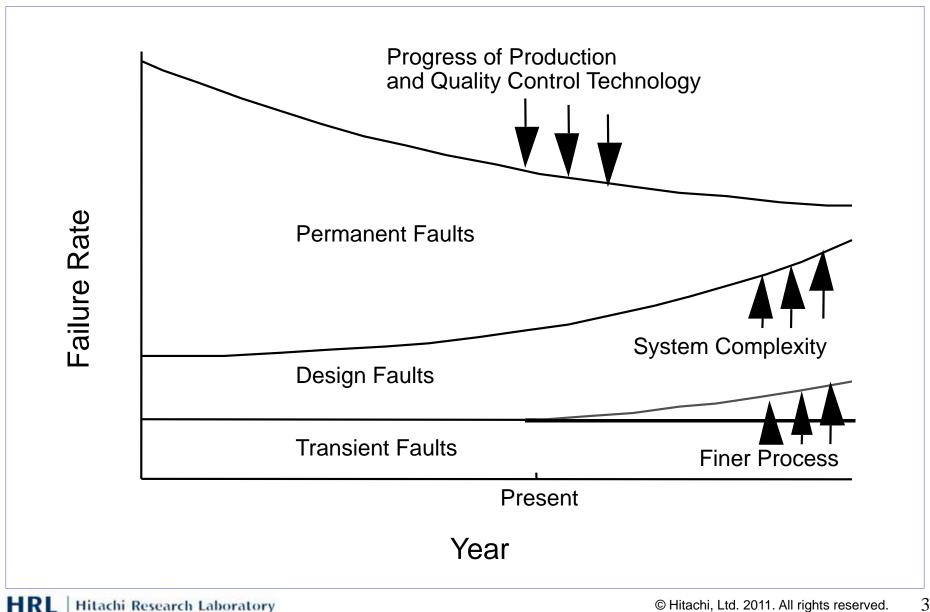

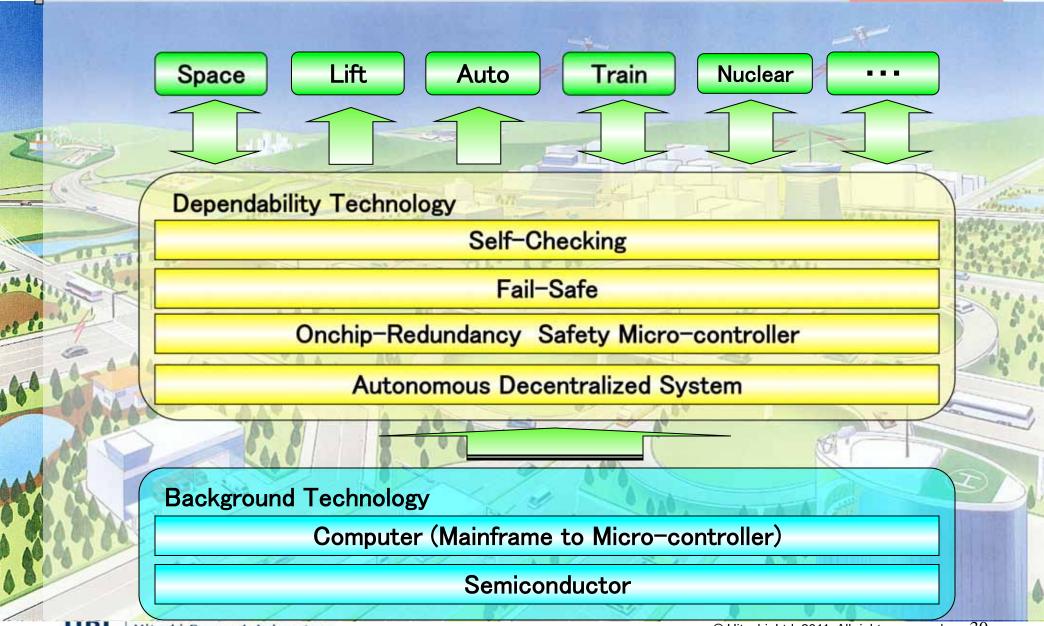

Integration of Semiconductor along with Moore's Law Causes;

- Terrestrial Neutron induced SEU's

- Synchronization Problem

- Electro-Magnetic Disturbance Sensitivity

Prospective Remedies;

- Intra-Board Redundancy

- On-chip Redundancy, and

- Consideration for Electro-Magnetic Disturbances (EMC, Power Integrity)

#### Reference includes Consideration for Electro-Magnetic

Disturbances;

Kanekawa et al., "Dependability in Electronic Systems: Mitigation of Hardware Failures, Soft Errors, and Electro-magnetic Disturbances," Springer (2010) ISBN-13: 978-1441967145

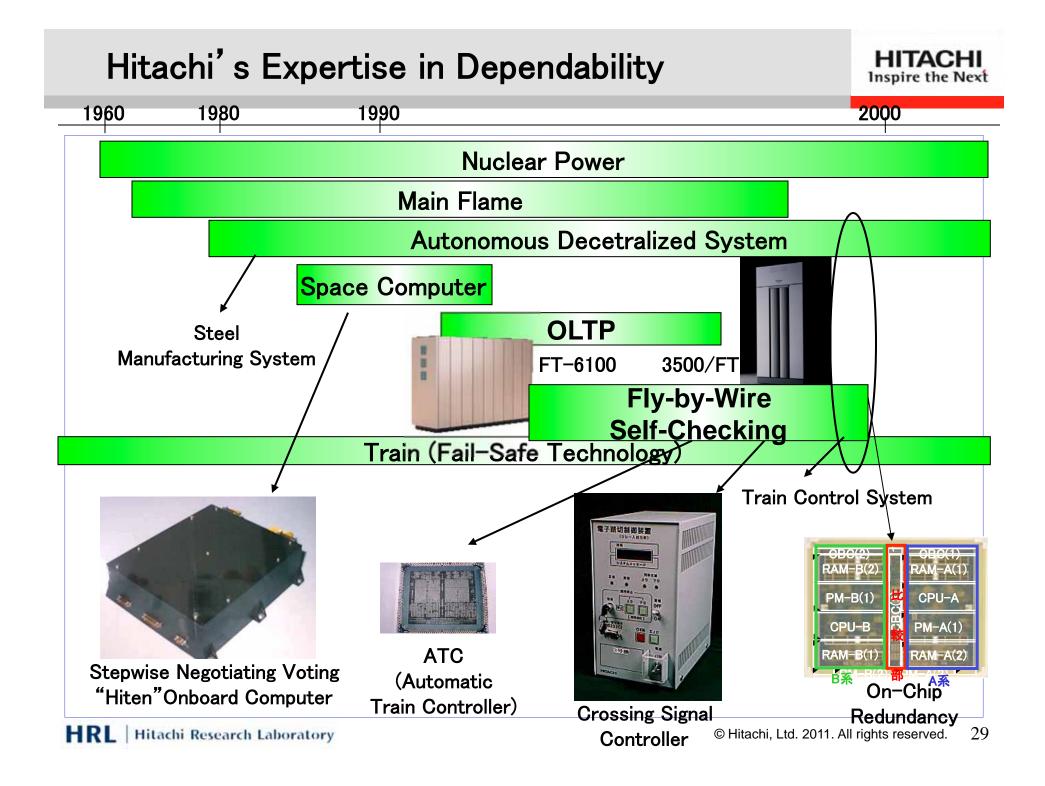

#### Hitachi's Approach for Dependability and Safety

HRL | Hitachi Research Laboratory

© Hitachi, Ltd. 2011. All rights reserved. 30

# HITACHI Inspire the Next

"安心と信頼の日立"

in Taiwan